- 您现在的位置:买卖IC网 > Sheet目录308 > ADZS-BF533-EZLITE (Analog Devices Inc)KIT W/BOARD EVAL FOR ADSP-BF533

ADSP-BF531 / ADSP-BF532 / ADSP-BF533

SPECIFICATIONS

Component specifications are subject to change

without notice.

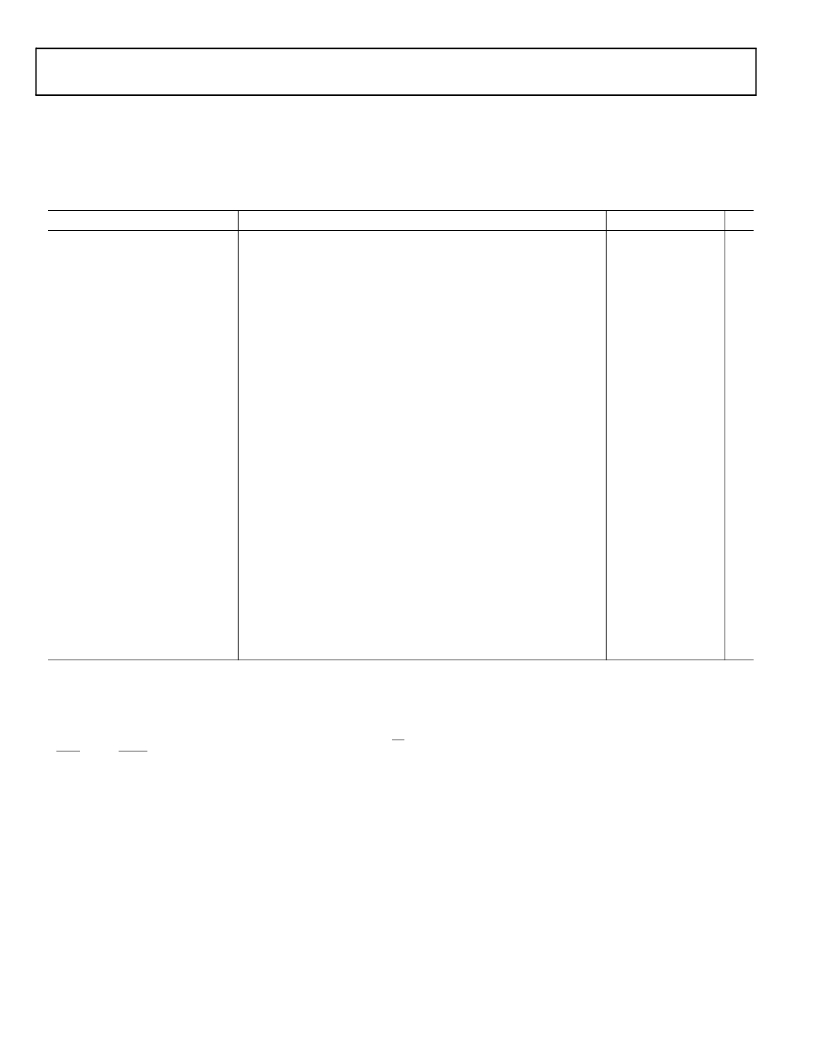

OPERATING CONDITIONS

Parameter

Conditions

Min Nominal

Max Unit

V DDINT Internal Supply Voltage

1

Nonautomotive 400 MHz and 500 MHz speed grade models

2

0.8 1.2

1.45

V

V DDINT Internal Supply Voltage

Nonautomotive 533 MHz speed grade models

0.8 1.25

1.45

V

V DDINT Internal Supply Voltage

600 MHz speed grade models

0.8 1.30

1.45

V

V DDINT Internal Supply Voltage 1

Automotive 400 MHz speed grade models 2

0.95 1.2

1.45

V

Automotive 533 MHz speed grade models

V DDINT Internal Supply Voltage

0.95 1.25

1.45

V

V DDEXT External Supply Voltage

V DDEXT External Supply Voltage

3

Nonautomotive grade models

Automotive grade models

1.75 1.8/3.3

2.7 3.3

3.6

3.6

V

V

V DDRTC Real-Time Clock

Nonautomotive grade models 2

1.75 1.8/3.3

3.6

V

Power Supply Voltage

V DDRTC Real-Time Clock

Automotive grade models 2

2.7 3.3

3.6

V

Power Supply Voltage

V IH

High Level Input Voltage 4, 5

V DDEXT =1.85 V

1.3

V

V IH

High Level Input Voltage

V DDEXT =Maximum

2.0

V

V IHCLKIN High Level Input Voltage

6

V DDEXT =Maximum

2.2

V

V IL

Low Level Input Voltage

7

V DDEXT =1.75 V

+0.3 V

V IL

Low Level Input Voltage 7

V DDEXT =2.7 V

+0.6 V

T J

Junction Temperature

160-Ball Chip Scale Ball Grid Array (CSP_BGA) @ T AMBIENT = 0°C to +70°C

0

+95

°C

T J

T J

Junction Temperature

Junction Temperature

160-Ball Chip Scale Ball Grid Array (CSP_BGA) @ T AMBIENT = –40°C to +85°C –40

160-Ball Chip Scale Ball Grid Array (CSP_BGA) @ T AMBIENT = –40°C to +105°C –40

+105 °C

+125 °C

T J

T J

T J

Junction Temperature

Junction Temperature

Junction Temperature

169-Ball Plastic Ball Grid Array (PBGA) @ T AMBIENT = –40°C to +105°C

169-Ball Plastic Ball Grid Array (PBGA) @ T AMBIENT = –40°C to +85°C

176-Lead Quad Flatpack (LQFP) @ T AMBIENT = –40°C to +85°C

–40

–40

–40

+125 °C

+105 °C

+100 °C

1

2

3

4

5

6

7

The regulator can generate V DDINT at levels of 0.85 V to 1.2 V with –5% to +10% tolerance, 1.25 V with –4% to +10% tolerance, and 1.3 V with –0% to +10% tolerance.

When V DDEXT < 2.25 V, on-chip voltage regulation is not supported.

Applies to all input and bidirectional pins except CLKIN.

The ADSP-BF531/ADSP-BF532/ADSP-BF533 processors are 3.3 V tolerant (always accepts up to 3.6 V maximum V IH ), but voltage compliance (on outputs, V OH ) depends on

the input V DDEXT , because V OH (maximum) approximately equals V DDEXT (maximum). This 3.3 V tolerance applies to bidirectional pins (DATA15–0, TMR2–0, PF15–0, PPI3–0,

RSCLK1–0, TSCLK1–0, RFS1–0, TFS1–0, MOSI, MISO, SCK) and input only pins (BR, ARDY, PPI_CLK, DR0PRI, DR0SEC, DR1PRI, DR1SEC, RX, RTXI, TCK, TDI, TMS,

TRST, CLKIN, RESET, NMI, and BMODE1–0).

Applies to CLKIN pin only.

Applies to all input and bidirectional pins.

Rev. I

|

Page 20 of 64 |

August 2013

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ADZS-BF538F-EZLITE

BOARD EVAL FOR ADSP-BF538

ADZS-BF561-EZLITE

BOARD EVAL ADSP-BF561

ADZS-BF592-EZLITE

KIT EVAL EZ LITE ADZS-BF592

ADZS-BF609-EZBRD

KIT EVAL EZ-BOARD ADSP-BF60X

ADZS-HPUSB-ICE

TOOL EMULATOR USB HP CROSSCORE

ADZS-ICE-100B

EMULATOR BLACKFIN

AK-Y1301

CABLE SCSI-3 EXTENSION 68CONDUCT

AK-Y1303

CABLE SCSI-3 ADAPTER 50CONDUCTOR

相关代理商/技术参数

ADZS-BF533-EZLITE

制造商:Analog Devices 功能描述:Microcontroller Development Tool

ADZS-BF533-MMSKIT

功能描述:KIT STARTER MULTIMEDIA BF533 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

ADZS-BF537-ASKIT

功能描述:BOARD EVAL SKIT ADSP-BF537 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

ADZS-BF537-EZLITE

功能描述:BOARD EVAL ADSP-BF537 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

ADZS-BF537-STAMP

功能描述:SYSTEM DEV FOR ADSP-BF537 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

ADZS-BF537-STAMP

制造商:Analog Devices 功能描述:Microcontroller Development Tool

ADZS-BF538-EZLITE

制造商:Analog Devices 功能描述:- Bulk

ADZSBF538FEZLITE

制造商:Analog Devices 功能描述:RES Wirewound 6927 75Ohm 1% 3W 20PPM SMD T/R